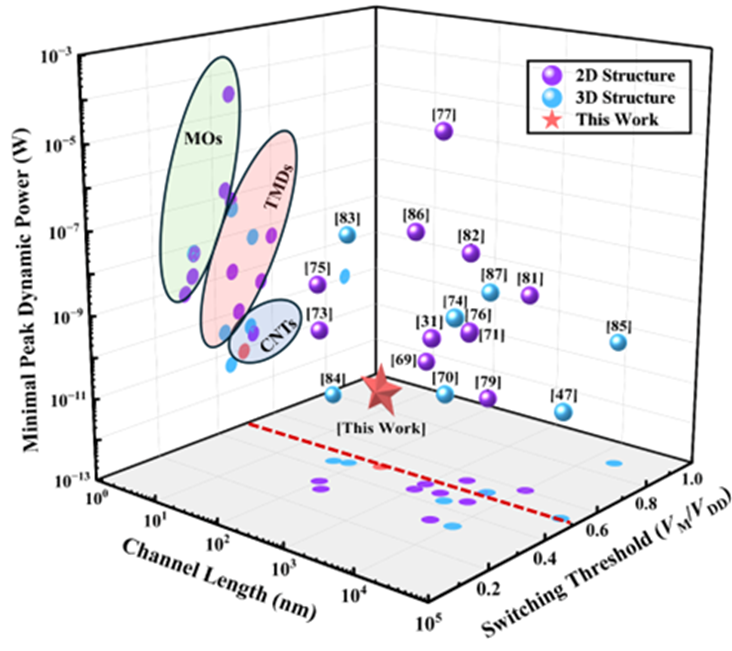

三维互补金属氧化物半导体(3D CMOS)技术是后摩尔时代集成电路的重要技术路线。山东省智能感知芯片与系统重点实验室陆芃教授团队创新性地提出一种碳纳米管/硅3D CMOS异质集成技术,通过在集成工艺流程中引入钴-60γ射线电离辐照工艺步骤,研制出超低功耗集成电路。本研究实现了8英寸晶圆180纳米工艺集成电路制备,并系统分析了作为数字电路基本单元的反相器的性能与可靠性。通过在三维集成中引入辐照工艺,可在无需对整体流程进行重大修改的情况下,解决P型与N型晶体管之间的阈值电压失配问题,反相器的最低研究电源电压(VDD)从0.5 V显著降低至0.2 V,功耗动态峰值较优化前降低831倍,实现了8.33 pW的超低动态功耗峰值,在已发表文献中处于最低水平之列。与此同时,3D CMOS反相器的实测开关阈值电压为0.495×VDD,接近0.5×VDD理想值,从而使反相器的低电平噪声容限提高35.1%,显著增强了数字电路单元的可靠性。

基于该研究成果的论文“Ionizing-irradiation-involved Integration of Ultra-low Power CNT-Si 3D CMOS ICs”近期发表在国际著名期刊Nano Research Energy(中科院1区TOP,2025年Cite Score 41.4)上(DOI:10.26599/NRE.2026.9120226)。本研究由本实验室温琦和陆芃教授团队、中国科学院微电子研究所李博研究员团队与南京大学朱马光教授团队合作完成。

论文链接:https://www.sciopen.com/article/10.26599/NRE.2026.9120226

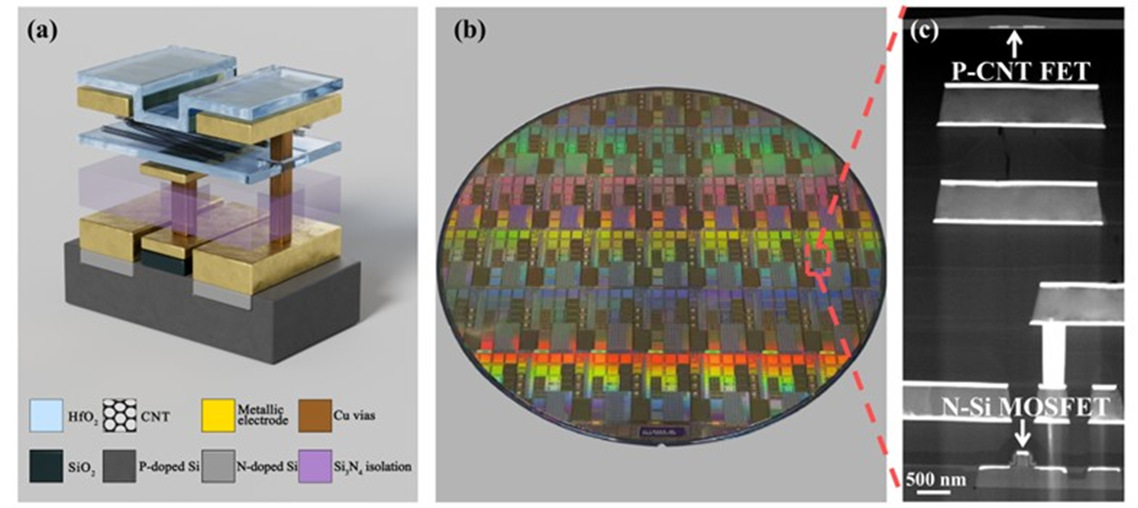

图1 碳纳米管/硅3D CMOS结构示意图与样品照片

图2 钴-60γ射线电离辐照工艺步骤示意图

图3 后摩尔集成电路技术功耗与可靠性对比